Gate-Treiber für GaN HEMTs

Mit zunehmender Komplexität und steigenden Anforderungsprofilen an leistungselektronische Schaltungen tritt das Gate-Treiber Design für GaN-HEMTs immer mehr in den Vordergrund und bildet einen elementaren Teil in der Forschung. Hierbei unterscheiden sie sich im Vergleich zu anderen WBG Halbleitern durch ihre steilen Schaltflanken sowie ihre geringen Schaltpegel. Dies führt im Gegenzug zu höheren Over- sowie Undershoots die im Design berücksichtig werden müssen. Die richtige Auslegung des Treibers bietet den Vorteil höhere Schaltfrequenzen, sowie steilerer Schaltflanken und geringerer Verluste. Damit einhergehend lässt sich ebenso eine Reduzierung der thermischen Belastung erreichen. Für die Reduzierung der Schaltverluste wird zusätzlich bei der Auslegung der Gate-Treiber der Einfluss des induktiven Feed Forward (iFF) untersucht.

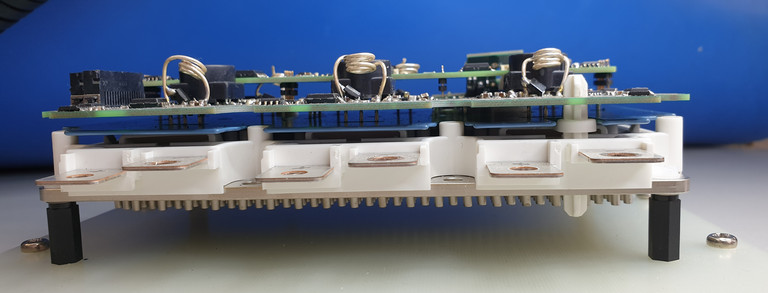

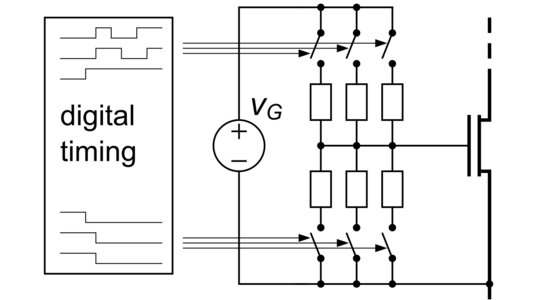

Adaptives Gatenetzwerk (Céline Lawniczak)

Zur Erforschung der Grenzen hinsichtlich der Schaltflanken und Schaltfrequenzen werden verschiedene diskrete Gate-Treiber untersucht, welche es ermöglichen den Gatewiderstand innerhalb einer Schaltflanke zu variieren. Durch das Einbinden diverser Widerstände sind entsprechend viele PWM Signale notwendig, welche aufeinander abgestimmt getaktet sein müssen. Zur Erstellung dieser wird ein Mikrocontroller in Kombination mit einem Complex Programmable Logic Device (CPLD) herangezogen, welche es ermöglichen im ns-Bereich zu agieren.

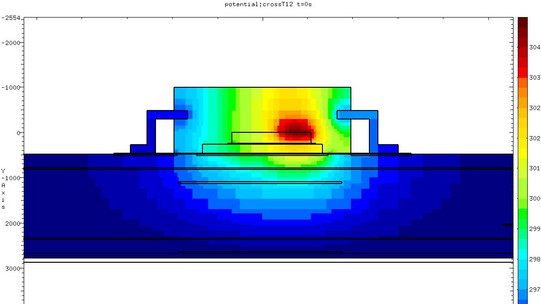

Lebensdauerüberwachung (Tim Egener)

Zur Überwachung der Komponenten wird in die Gate-Treiber-Schaltung eine Messtechnik integriert, welche die elektrisch messbaren Größen aufnimmt. Auf dieser Basis wird ein Digital-Twin-Ansatz abgeleitet, um den Betriebszustand des Leistungshalbleiter sowie seinen Alterungszustand zu ermitteln (Condition Monitoring). Hierfür liegen Modelle zugrunde, welche die Thresholdspannung und die Chiptemperatur im laufenden Betrieb ermitteln. Hiermit soll ermöglicht werden die Möglichkeiten der Leistungshalbleiter weiter auszuschöpfen und eine Überdimensionierung zu vermeiden.

Totzeitenregulierung (Lukas Knappstein)

Geforscht wird an der Verwendung von GaN-HEMTs in Halbbrücken. Da die Totzeit (Schaltpause beim Schaltvorgang zweier Transistoren) einen großen Einfluss auf die Effizienz hat, wird an Totzeitenregelungen geforscht. Schwerpunkt liegt hierbei im Entwurf eines adaptiven Totzeitenreglers mit Bezug auf Signalmuster, die unabhängig der verwendeten Bauteile erkennbar sind. Vorteil dabei ist, dass ein diskretes Anlernen von Kennfeldern dadurch obsolet wird. Außerdem können solche Kennfelder Unsicherheiten bzgl. Veränderungen des Systems (Durch Temperatur, Alterung, etc.) aufweisen. Dafür wird an hochfrequenten Messtechniken geforscht. Herausforderung ist, entsprechende Signale so wenig invasiv und dabei durch so simple Prinzipien wie nur möglich messen zu können.

- Entwicklung von schnellschaltenden Multilevel Ansteuerverfahren

- Messung von Betriebszuständen zur Überwachung der Lebensdauer

- Messdaten Auswertung auf Gate-Treiber mit A/D- Wandlern und FPGAs

- Einbettung des iFF-Verfahrens zur Reduzierung der Schaltverluste