Gate-Treiber für SiC MOSFETs

Aufgrund der steigenden Anforderungen an Effizienz und Leistungsdichte in der Leistungselektronik gewinnen SiC-MOSFETs zunehmend an Bedeutung. Gate-Treiber spielen dabei eine zentrale Rolle, da sie durch schnelles und präzises Ansteuern die Schaltverluste reduzieren und die Gesamtperformance der Bauelemente verbessern. Durch optimierte Gate-Ansteuerung lassen sich zudem Überschwinger und elektromagnetische Störungen minimieren, was die Systemzuverlässigkeit erhöht. Moderne Gate-Treiber bieten darüber hinaus Diagnose- und Monitoringfunktionen, die Zustände wie Kurzschluss oder Übertemperatur erkennen und so einen sicheren und effizienten Betrieb ermöglichen.

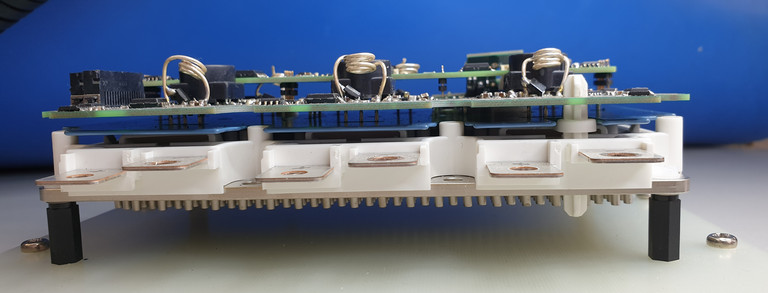

Aktive Gate-Treiber-Netzwerke (Lukas Kappel, Oliver Moss, Niklas Falkenberg)

Wide-Bandgap Leistungshalbleiterbauelemente wie z.B. Siliziumkarbid (SiC) MOSFETs ermöglichen höhere Schaltfrequenzen und geringere Schaltverluste bei höheren Betriebsspannungen- und strömen. Die hohen Schaltgeschwindigkeitenführen jedoch zu Überschwingern und parasitären Schwingungen, die wiederum zu erhöhten Verlusten und zu elektromagnetischen Störungen führen. Dies begrenzt die tatsächlich mögliche Schaltgeschwindigkeit. Um die Vorteile von SiC MOSFETs besser nutzen zu können, wird ein aktives Gate-Treiber-Netzwerk benötigt, welches eine Modulation des Gate-Source Signales ermöglicht. Dadurch können schnelle Schaltgeschwindigkeiten als auch geringere Überschwinger und parasitäres Schwingen realisiert werden.

Zustandsüberwachung mit digitalem Zwilling

Zur Überwachung und Regelung von Leistungselektronik wird ein kompakter digitaler Zwilling von SiC MOSFETs abgeleitet, welcher über die am Gate-Treiber angesiedelte, fortschrittliche Messtechnik mit weiteren Informationen versorgt wird. Anhand von den Messdaten und den Prognosen des digitalen Zwillings können Prognostic Health Management (PHM)-Funktionen während des Betriebs den sicheren Betriebsbereich kalkulieren, um das volle Potenzial von SiC MOSFETs auszuschöpfen.

- Messung von Betriebszuständen zur Überwachung des Abstandes der Arbeitspunktes zum sicheren Betriebsbereich (Safe Operating Area)

- Entwicklung von schnellschaltenden Systemen mit Wide-Bandgap SiC Transistoren

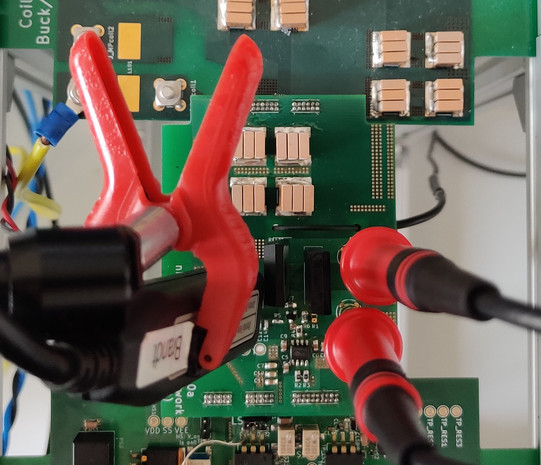

- Erstellung einer Doppelpulsmessung zur Validierung und Verifikation des Schaltverhaltens einer induktiven Last

- Entwicklung von modulierten Gate-Treibersignalen für schnellschaltende Systeme

- Einbettung des iFF-Verfahrens zur Reduzierung der Schaltverluste

Kontakt

Publikationen

Choo, V.L.; Pfost, M.: A Variable Gate Resistance SiC MOSFET Driver Network to Mitigate Overshoot and Parasitic Ringing, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe 2023), Nürnberg, Germany, 05.2023, DOI: 10.30420/566091153