AI4CSM

Automotive Intelligence 4 Connected Shared Mobility

Gatetreiber mit autonomen Effizienz- und Sicherheitsfunktionen für GaN Leistungshalbleiter

Nicht nur die Nachfrage an Mobilität insbesondere im Individualverkehr steigt, sondern auch die Anforderungen an die Klimaneutralität. Daher ist in diesem internationalen Projekt das Ziel, ein elektrisch und autonom fahrendes Fahrzeug zu entwickeln, mit dem eine kostengünstigere, schnellere und umweltfreundlichere Fortbewegung möglich sein wird.

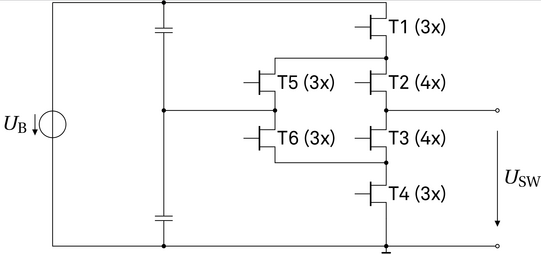

Der Lehrstuhl für Energiewandlung arbeitet dafür mit neuartigen GaN-HEMT Transistoren. Dabei ermöglicht das Verwenden von GaN-HEMTs aufgrund besserer Elektronenmobilität und niedrigerer parasitärer Kapazitäten kürzere Schaltvorgänge und damit eine Steigerung der Effizienz. Aufgrund der niedrigeren Spannungsfestigkeit der GaN-HEMTs von 650V als das Bordspannungsniveau von 800V wird an einem neuartigen Inverter mit 3L-ANPC Struktur geforscht, in der sechs GaN-HEMTs kaskodiert verschaltet werden. Durch die Steigerung der Effizienz kann nicht nur der Energiebedarf gesenkt werden, sondern auch der Platzbedarf, sowie eine höhere Leistungsabgabe ermöglicht werden.

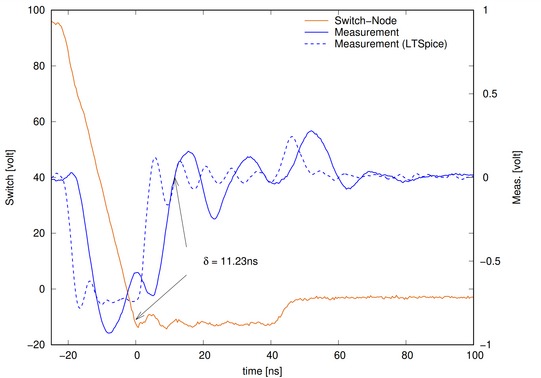

Das Einstellen von Schalt-Totzeiten ist von essentieller Bedeutung, da ein Umschaltvorgang entweder zu Querströmen führen kann, oder ein Transistor kurzzeitig rückwärts leitet. Die Herausforderung liegt in der Komplexität der 3L-ANPC Struktur, sowie des wechselhaften Arbeitsbereichs im Automobil, was ein statisches Einstellen der Totzeiten nicht mehr zulässt.

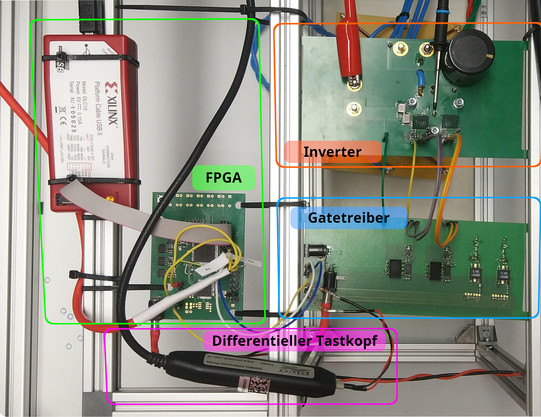

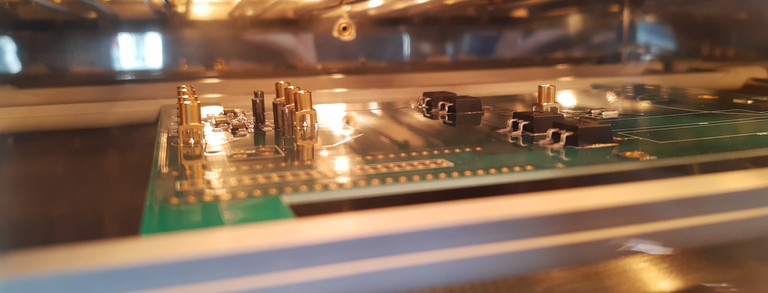

Daher wird an der TU Dortmund an einem Gatetreiber mit adaptiver Totzeitenregulierung geforscht, sodass keine aufwendigen Modell- und Kennfeldbasierten Steuerungen notwendig sind. Dabei liegt der Forschungsschwerpunkt bei der Verwendung einer hochempfindlichen und -frequenten Messtechnik. Zur entsprechenden Interpretation der Daten sollen verschiedene Ansätze erforscht werden, wie zum Beispiel neuronale Netze oder auch Frequenzanalysen.

- Sichere Handhabung eines 3L-ANPC Inverters mit 6 GaN-HEMTs pro Phase

- Messung durch eigene Messtechnik mit FPGA und AD-Wandlern

- Interpretation der Messdaten zu folgenden Zwecken:

- Fehlererkennung eines Transistors ohne Beschädigung weiterer Transistoren

- Effizienzsteigerung durch Regelung zum optimalen Arbeitsbereich

- Betrachtung der Schaltflanken in Bezug auf elektromagnetische Verträglichkeit

Dieses Projekt wird durch das Bundesministerium für Bildung und Forschung (BMBF) unter der Förderkennung 16ME0175 gefördert.